RAM & ROM

RAM(Random Access Memory): 휘발성 저장장치

| RAM의 종류 | 설명 |

| DRAM (Dynamic RAM) | 시간이 지나면 점차 저장된 데이터가 사라지는 RAM 메인 메모리에서 주로 사용되는 RAM |

| SRAM (Static RAM) | 시간이 지나도 저장된 데이터가 사라지지 않는 RAM 캐시 메모리에서 주로 사용되는 RAM (얘도 휘발성임) |

| SDR SDRAM (SynchromousDynamic RAM) | 클럭과 동기화된 RAM 클럭의 타이밍에 맞춰 CPU와 정보를 주고받을 수 있는 RAM (SDR: SingleData Rate RAM) |

| DDR SDRAM (Double Data Rate SDRAM) | 대역폭을 넓혀 속도를 높인 RAM SDRAM |

| DDR2 SDRAM (SDR*4) | SRD에 4배 대역폭 |

| DDR3 SDRAM (SDR*8) | SRD에 8배 대역폭 |

ROM (Read Only Memory): 부팅시

| ROM의 종류 | 설명 |

| Mask ROM | 가장 기본적인 형태의 ROM 제조 과정에서 저장할 내용을 미리 기록 |

| PROM(Programmable ROM) | 데이터를 한 번 새길 수 있는 ROM 한 번에 한해 사용자가 직접 원하는 데이터를 써넣을 수 있는 ROM |

| EPROM (Erasable PROM) | 지우고 다시 저장 가능한 PROM 자외선 혹은 전기를 이용해 지우기 가능 |

| 플래시 메모리 | EEPROM의 발전된, 저렴한 형태, 반도체 기반의 저장장치 |

*이론상 CPU+보조기억장치 가능은 함 | CPU 접근속도 빠른 순서: 레지스터 > 메인메모리 > 보조기억장치

리틀 엔디안과 빅 엔디안

메모리에 데이터를 밀어넣는 순서

• 일반적으로 메모리는 바이트 단위로 저장

• 하지만 CPU로부터 메모리가 받아들이는 데이터는 4 바이트(32 비트), 혹은 8 바이트 (64 비트) 워드(Word) 단위

• 1 바이트씩 저장하는 메모리의 경우 : 4바이트 데이터는 네 개의 주소에 걸쳐 저장

• 1 바이트씩 저장하는 메모리의 경우 : 8바이트 데이터는 여덟 개의 주소에 걸쳐 저장

빅 엔디안

낮은 번지 주소부터 저장하는 방식 (MSB부터 저장)

리틀 엔디안

높은 번지 주소부터 저장하는 방식 (LSB부터 저장)

*리틀 엔디안을 많이 씀. (계산의 용이성)

*단, 로컬 하드웨어에서는 리틀 엔디안으로 읽고 쓰지만, 네트워크 전송시에는 빅 엔디안으로 통일.

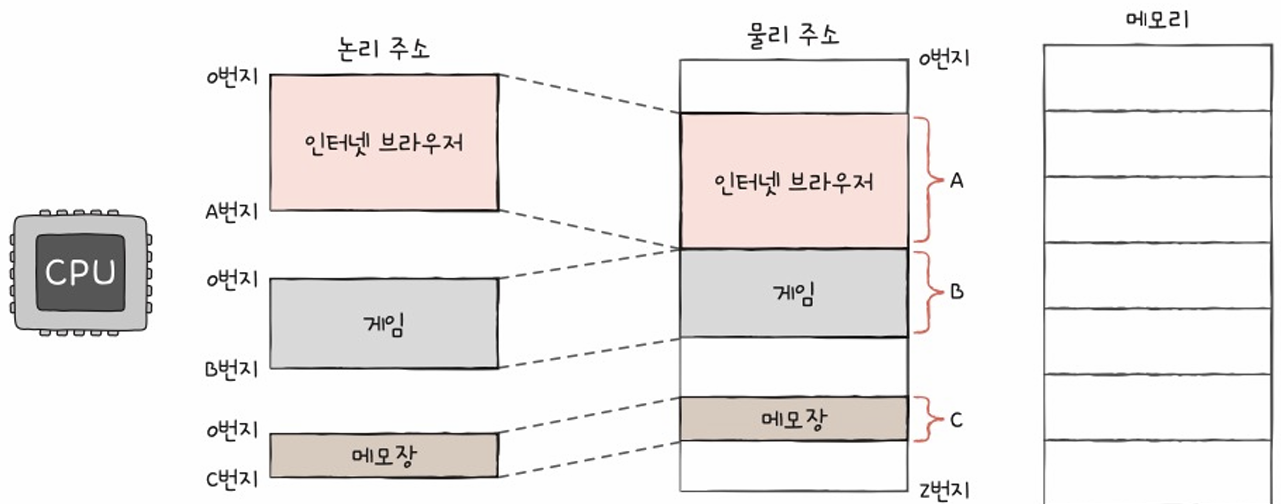

주소 공간 - 논리 주소와 물리 주소

• 물리 주소: 실제 메모리의 하드웨서상의 주소

• 논리 주소: CPU와 실행 중인 프로그램이 사용하는 주소 (0번지부터 시작)

CPU는 실행 중인 프로그램이 현재 실제 물리적 메모리 몇 번지에 무엇이 저장되어 있는지 모른다.

CPU는 논리 주소 활용

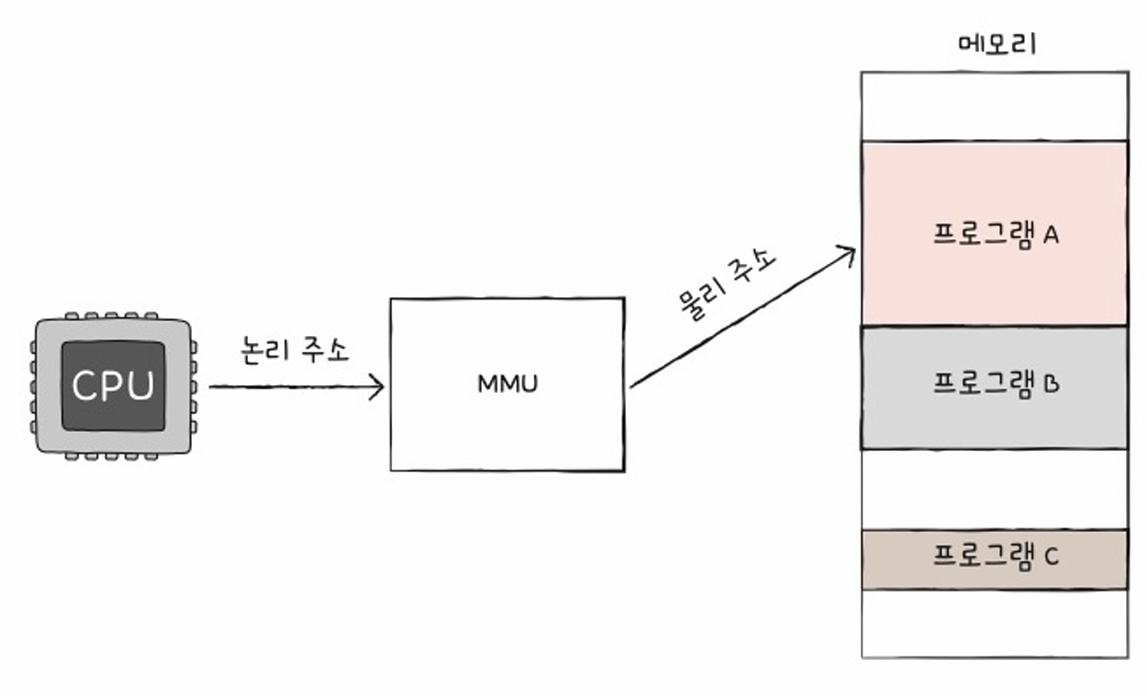

*주소 변환

CPU/프로그램이 사용하는 주소 체계(논리 주소)와

메모리가 사용하는 주소 체계(물리 주소)가 다르다면 어떻게 문제없이 부품 간 통신이 가능할까?

MMU(Memory Managament Unit) 를 활용해서 논리주소를 물리주소로 변환

*MMU의 기본 동작

베이스 레지스터를 활용한 주소 변환

베이스 레지스터 = 기준 주소

논리 주소 = 기준 주소로부터 떨어진 거리

한계 레지스터로(프로그램 크기가 등록된 레지스터) CPU의 잘못된 요청을 막을 수 있음.

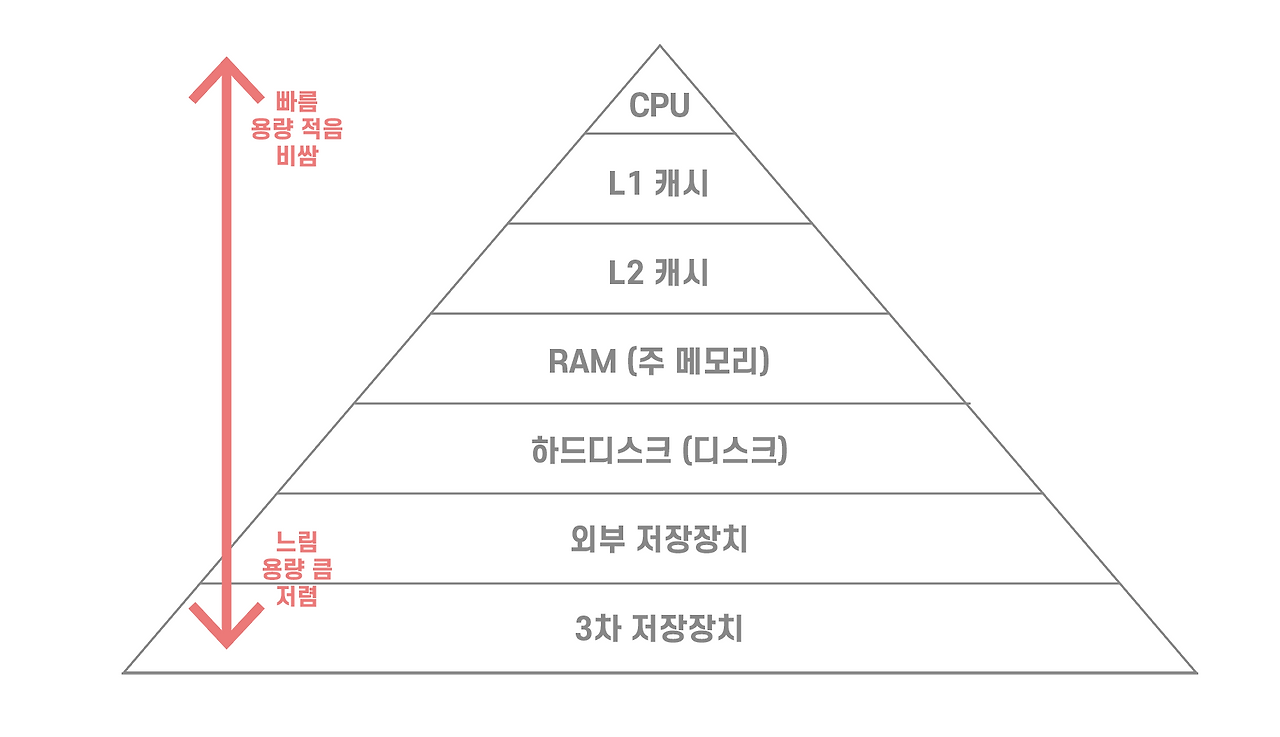

저장 장치 계층 구조와 캐시 메모리

CPU와 멀어질수록 달라지는 저장장치의 특성 (멀수록 용량 커지고 속도 느려짐)

• 레지스터 vs 메인 메모리

• 메인 메모리 vs 보조기억장치

• 보조기억장치 vs 클라우드 저장 장치

CPU(레지스터) → 캐시 → DRAM

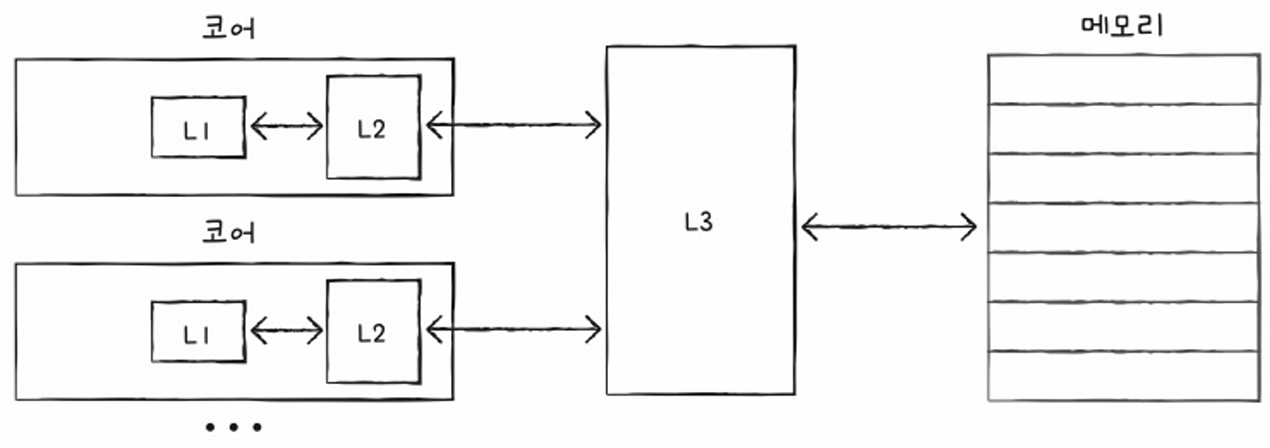

캐시 메모리

• CPU와 메모리 간의 속도 차를 극복하기 위해 탄생

• CPU와 메모리 사이에 위치, 레지스터보다 용량이 크고 메모리보다 빠른 SRAM 기반

• CPU에서 사용할 법한 정보를 미리 가져와 저장

• 메모리가 대형 마트라면 캐시 메모리는 편의점

• L1(Level 1) 캐시 메모리 CPU와 가깝고 용량 작음

• L2(Level 2) 캐시 메모리

• L3(Level 3) 캐시 메모리 CPU와 멀고 용량 큼

L1-L2는 코어 안에 있음. 멀티 코어의 경우 L3로 코어끼리 공유

CPU가 필요료 하는 값이 캐시 메모리에 있는 경우: 캐시 히트

CPU가 필요료 하는 값이 캐시 메모리에 없는 경우: 캐시 미스

캐시 히트율: 요즘 70%~90%수준

캐시 메모리는 어떤 데이터를 저장할까?

→ CPU가 자주 사용할 법한 내용

→ 그렇다면 CPU가 자주 사용할 법한 내용은 어떻게 예측할까?

→ 참조 지역성의 원리 (locality of reference)

참조 지역성의 원리

1. 시간 지역성: 최근에 접근했던 메모리 공간에 다시 접근하려는 경향.

2. 공간 지역성: CPU는 접근한 메모리 공간 근처를 접근하려는 경향.